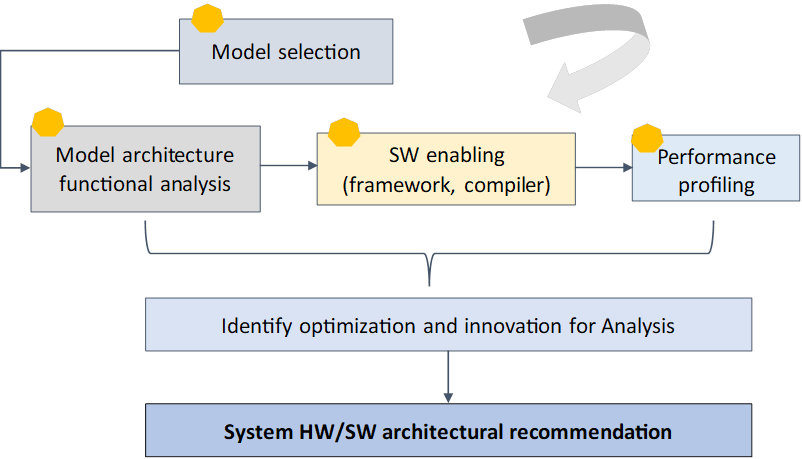

Dobbiamo progettare HW efficienti “SW/algorithm aware” e SW/algoritmi “HW aware”, in modo che possano intrecciarsi strettamente per spremere ogni bit delle nostre risorse di elaborazione limitate. Come dovremmo farlo? Di seguito è riportata una metodologia in evoluzione che può essere utilizzata come riferimento se si stanno progettando nuove funzionalità HW/SW per l’intelligenza artificiale.

1. Identificare i carichi di lavoro AI proxy.

Per avviare l’analisi, abbiamo bisogno di modelli di intelligenza artificiale proxy e di definire un elenco di priorità per indagare ulteriormente. Esistono molteplici risorse a cui puoi fare riferimento, incluso l’ultimo documento di ricerca (CVPR, Siggraph, laboratori di ricerca di grandi tecnologie) con codice open source, feedback o richieste dei clienti, tendenze del settore, ecc. Filtra diversi modelli rappresentativi in base al tuo esperto giudizio. Questo passaggio è fondamentale poiché li utilizzerai per progettare la tua “architettura futura”

2. Analisi approfondita dell’architettura del modello.

Assicurati di analizzare l’architettura del modello in modo completo per comprenderne la funzionalità, l’innovazione e scomporla il più possibile in parti dettagliate. Ci sono nuovi operatori non supportati nell’attuale stack tecnologico? Dove sono i livelli ad alta intensità di calcolo? È un modello pesante per il trasferimento di dati (memoria)? Qual è il tipo di dati richiesto e che tipo di tecniche di quantizzazione possono essere applicate senza sacrificare la precisione? Quale parte del modello può essere accelerata dall’hardware e dove sono le potenziali ottimizzazioni delle prestazioni?

Ad esempio, nel rendering neurale, il modello richiede sia il rendering che il calcolo (moltiplicazione di matrice) che lavorano in parallelo, è necessario verificare se lo stack SW corrente supporta il rendering/calcolo simultaneamente. Negli LLM, la dimensione della cache dei valori-chiave (KV) aumenta rispetto alla lunghezza della sequenza di input, è fondamentale comprendere i requisiti di memoria e la potenziale ottimizzazione del trasferimento dati/gerarchia di memoria per gestire cache KV di grandi dimensioni.

3. Abilitazione e prototipazione SW

Scarica il codice open source per il modello identificato nel passaggio 2 ed eseguilo sul framework SW/HW “di destinazione”. Questo passaggio non è semplice, soprattutto per i modelli nuovi/dirompenti. Poiché l’obiettivo è abilitare una soluzione praticabile per l’analisi delle prestazioni, in questa fase non è necessario fornire un codice di qualità del prodotto. Una correzione sporca del SW senza regolazione delle prestazioni è accettabile per procedere al passaggio 4. Un passaggio importante consiste nel convertire il modello pre-addestrato nel framework di sviluppo (Pytorch) in un nuovo formato richiesto dal nuovo framework di destinazione.

torch.onnx.export(model,

dummy_input,

"resnet50.onnx",

verbose=False,

input_names=input_names,

outputnames=output_names,

export_params=True)

Tuttavia, ci sono spesso casi in cui è necessario uno sforzo di supporto significativo. Ad esempio, per eseguire modelli di rendering differenziabili, è necessario supportare autograd. È molto probabile che questa funzionalità non sia pronta nel nuovo framework e richieda mesi di impegno da parte del team di sviluppo. Un altro esempio è la quantizzazione GPTQ per LLM, che inizialmente potrebbe non essere supportata nel quadro di inferenza. Invece di aspettare il team di ingegneri, gli architetti possono eseguire il carico di lavoro sul sistema Nvidia per l’analisi delle prestazioni, poiché Nvidia è la scelta dell’hardware per lo sviluppo accademico. Ciò consente lo sviluppo di un elenco di requisiti SW in base alle lacune osservate durante l’abilitazione del SW.

4. Analisi delle prestazioni e innovazione architetturale.

Esistono numerosi parametri per giudicare le prestazioni di un modello di intelligenza artificiale. Di seguito sono riportati i principali che dovremmo considerare.

4.1 FLOP (Operazioni in virgola mobile) e MAC (Operazioni di moltiplicazione-accumulo).

Queste metriche sono comunemente utilizzate per calcolare la complessità computazionale dei modelli di deep learning. Forniscono un modo semplice e veloce per comprendere il numero di operazioni aritmetiche richieste. I FLOP possono essere calcolati tramite metodi come analisi cartacea, report Vtune o strumenti come flops-counter.pytorch e pytorch-OpCounter.

4.2 Impronta di memoria e larghezza di banda (BW)

L’impronta della memoria è costituita principalmente da pesi (parametri di rete) e dati di input. Ad esempio, un modello Llama con parametri 13B in FP16 consuma circa 13*2 (FP16=2 byte) = 26 GB di memoria (l’input è trascurabile poiché il peso occupa molto più spazio). Un altro fattore chiave per gli LLM è la dimensione della cache KV. La cache KV occupa fino al 30% della memoria totale ed è dinamica (fare riferimento all’immagine al passaggio 2). I modelli di grandi dimensioni sono generalmente legati alla memoria poiché la velocità dipende dalla velocità con cui si spostano i dati dalla memoria di sistema alla memoria locale o dalla memoria locale alle cache/registri locali. La memoria disponibile BW è molto migliore nel prevedere la latenza di inferenza (tempo di generazione di token per LLM) rispetto ai TOPS di calcolo di picco. Un indicatore delle prestazioni è l’utilizzo della larghezza di banda della memoria (MBU), definito come BW effettivo/BW di picco. Idealmente, un MBU vicino al 100% indica che il BW della memoria è completamente utilizzato.

La memoria sufficiente non è sufficiente!

Poiché la memoria rappresenta un collo di bottiglia, è necessaria l’esplorazione delle tecnologie avanzate di compressione dei modelli e di memoria/caching. Alcune opere pionieristiche sono elencate di seguito:

- MemGPT: utilizza risorse di gerarchia di memoria a diversi livelli, come una combinazione di RAM veloce e piccola e memoria di archiviazione grande e lenta. Le informazioni devono essere trasferite esplicitamente tra di loro. (2)

- Quantizzazione a bassa precisione (GPTQ, AWQ, GGML) per ridurre l’ingombro della memoria dei modelli

- In-memory computing (PIM): riduce il consumo energetico e migliora le prestazioni eliminando la necessità di spostare i dati.

4.3 Latenza/velocità effettiva.

Nella visione artificiale, la latenza è il tempo necessario per generare un fotogramma. Nel contesto degli LLM, è il tempo che intercorre tra il primo token e la successiva generazione di token. Il throughput è il numero di token/frame al secondo. La latenza è una metrica fondamentale per misurare le prestazioni del sistema AI ed è un fattore composto dalle prestazioni SW/HW. Esistono varie strategie di ottimizzazione da considerare, per citarne alcune di seguito:

- Ottimizzazione delle operazioni con vincoli di larghezza di banda come normalizzazioni, operazioni puntuali, SoftMax e ReLU. Si stima che la normalizzazione e le operazioni puntuali consumino quasi il 40% in più di tempo di esecuzione rispetto alle moltiplicazioni di matrici, ottenendo rispettivamente solo 250x e 700x FLOPS in meno rispetto alle moltiplicazioni di matrici. Per risolvere il problema, la fusione del kernel può essere utilizzata per fondere più operatori per risparmiare sui costi di trasferimento dei dati o sostituire operatori costosi (softmax) con quelli leggeri (ReLU).

- Architettura HW specializzata. L’integrazione di hardware specializzato (AVX, GPU, TPU, NPU) può portare a notevoli accelerazioni e risparmi energetici, il che è particolarmente importante per le applicazioni che richiedono elaborazione in tempo reale su dispositivi con risorse limitate. Ad esempio, le istruzioni Intel AVX possono portare ad una velocità fino a 60.000 volte maggiore rispetto al codice Python nativo.

I tensor core sulla grafica Nvidia (V100, A100, H100, ecc.) possono moltiplicare e aggiungere due matrici FP16 e/o FP32 in un ciclo di clock, rispetto ai core Cuda che possono eseguire solo 1 operazione per ciclo. Tuttavia, l’utilizzo del tensor core è molto basso (3%-9% per la formazione end-to-end), con conseguenti costi energetici elevati e basse prestazioni. È in corso una ricerca attiva sul miglioramento dell’utilizzo degli array sistolici (FlexSA, SA multidirezionale, ecc.) di cui scriverò nella prossima serie di post.

Inoltre, poiché la memoria e il traffico dati rappresentano sempre un collo di bottiglia per i modelli di intelligenza artificiale di grandi dimensioni, è fondamentale esplorare un’architettura avanzata considerando una memoria su chip più grande ed efficiente. Un esempio è il design della memoria core di Cerebras, in cui la memoria viene indirizzata in modo indipendente per core.

- Esistono molte altre ottimizzazioni: parallelismo, quantizzazione della cache KV per LLM, attivazione sparsa e ottimizzazione end-to-end: spiegherò di più nei prossimi post

4.4 Potenza ed efficienza energetica

La potenza è un’altra bestia che dobbiamo esaminare, soprattutto per gli scenari di utenti a basso consumo. È sempre un compromesso tra prestazioni e potenza. Come illustrato di seguito, l’operazione di accesso alla memoria richiede un paio di ordini di grandezza in più di energia rispetto alle operazioni di calcolo. La riduzione del trasferimento di memoria è fortemente necessaria per risparmiare energia.

Fonte: towardsdatascience.com